【VHDL】デコーダ回路

3to8デコーダ回路

以下に,3to8デコーダ回路のVHDLソースコードを表示する.

-- Barrel Shifter used Decoder library IEEE; use IEEE.std_logic_1164.all; entity Decoder3to8 is port ( CBA : in std_logic_vector(2 downto 0); D : out std_logic_vector(7 downto 0) ); end Decoder3to8; architecture RTL of Decoder3to8 is component BShifterNbit generic (N : integer); port ( A : in std_logic_vector((2**N) - 1 downto 0); S : in std_logic_vector(N - 1 downto 0); Z : out std_logic_vector((2**N) - 1 downto 0) ); end component; constant N : integer := 3; signal tA : std_logic_vector((2**N) - 1 downto 0); begin tA <= "00000001"; SHIFTER : BShifterNbit generic map (N) port map (tA, CBA, D); end RTL;

バレルシフタを使用して,デコーダ回路を作成しています.

バレル・シフト回路&パリティ回路&デコーダ回路のテストベンチ

以下に,3つの回路をテストするテストベンチを示す.

library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_arith.all; use IEEE.std_logic_unsigned.all; entity TestBench_Parity is end TestBench_Parity; architecture TestBench of TestBench_Parity is component Decoder3to8 port ( CBA : in std_logic_vector(2 downto 0); D : out std_logic_vector(7 downto 0) ); end component; component ParityNbit generic (N : integer); port ( A : in std_logic_vector(N - 1 downto 0); P : out std_logic ); end component; constant N : integer := 8; signal CBAin : std_logic_vector(2 downto 0); signal Dout : std_logic_vector(7 downto 0); signal Pout : std_logic; begin DUT0 : Decoder3to8 port map (CBAin, Dout); DUT1 : ParityNbit generic map (N) port map (Dout, Pout); generator : process begin CBAin <= "000"; wait for 10 ns; for I in 1 to 100 loop CBAin <= CBAin + 1; wait for 10 ns; end loop; end process; end TestBench;

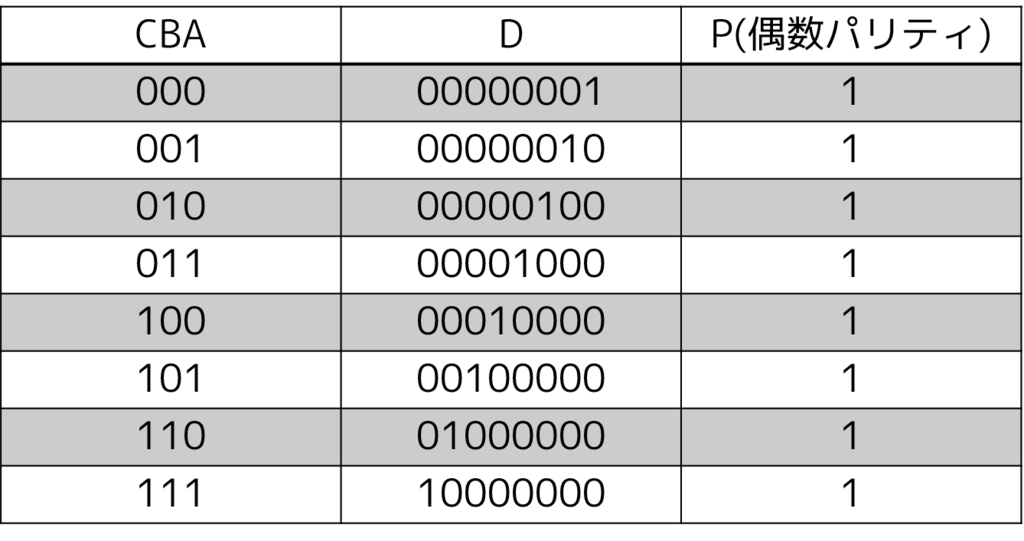

テストベンチの真理値表

以下の真理値表に基づき,テストベンチを作成した.